ISP-programmer to AVR synchronisation

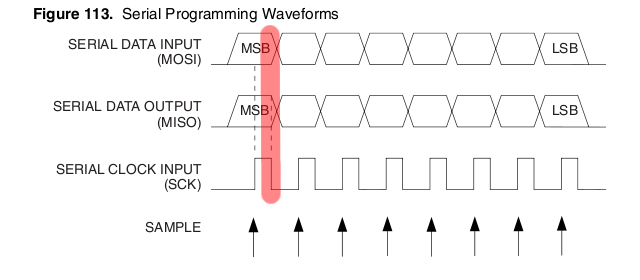

AVR ISP-programming starts with RESET activation following by transmitting of programming enable instruction. Entry sequence requirement is that SCK must be set to ‘0’ during RESET activation. Otherwise SCK falling edge causes unintended programming hardware state change.

The falling edge distorts 4-byte programming instruction. The microcontroller does not recognise it and does not enter programming mode. There is no sense to send programming entry instruction again because byte-level command’s phase is shifted by one SCK period. The last SCK pulse of previous instruction will act as extra pulse for subsequent command.

Synchronisation can also be corrupted during programming process. Read more in publication about AVReAl “synchronisation lost” message.

Atmel datasheets describe two methods for synchronisation recovery.

The first method uses additional SCK pulse after non-successful program entry command. That way byte-oriented command packet is shifted by one bit until the microcontroller recognises the command.

Low-voltage Serial Programming Algorithm

…

3. The serial programming instructions will not work if the communication is out of synchronization. When in sync, the second byte ($53) will echo back when issuing the third byte of the Programming Enable instruction. Whether the echo is correct or not, all four bytes of the instruction must be transmitted. If the $53 did not echo back,give SCK a positive pulseand issue a new Programming Enable instruction. If the $53 is not seen within 32 attempts, there is no functional device connected.

The first method is described in datasheets for AT90S4433, AT90S8515, ATtiny12, ATtiny15, ATtiny22, ATmega163 and older micros.

For ATtiny13, ATtiny26, ATmega8, … ATmega128 and newer it is recommended a second one:

Serial Programming Algorithm

…

3. The Serial Programming instructions will not work if the communication is out of synchronization. When in sync. the second byte (0x53), will echo back when issuing the third byte of the Programming Enable instruction. Whether the echo is correct or not, all four bytes of the instruction must be transmitted. If the 0x53 did not echo back,give RESET a positive pulseand issue a new Programming Enable command.

Thus datasheets recommend the synchronisation recovery method with RESET pulse for all modern AVR micros. RESET acts as Chip Select input for programming hardware.

There is a resynchronisation method flag in AVReAl chip description table. So AVReAl uses suitable method for each AVR microcontroller.

However the second method is not a resynchronisation method. It is just repeating of programming enable sequence “reset and send instruction”.

Let a microcontroller is programmed with a code that set active high level on SCK pin. That is “SCK must be low during reset activation” requirement does not meet. Programming enable instruction will fail. The programmer will apply a positive pulse on RESET pin and send a new programming instruction. If the microcontroller has enough time to set high level on SCK again than a new programming enable instruction will fail again.

AVReAl attempts to lower probability of scenario described above by making RESET pulse width about a few core clock periods. It uses core clock frequency from -o switch.

There is a discrete change in the pulse width determined by a specific hardware programmer. Firmware can change core clock frequency. In some cases RESET pulse might not help. However this situation happens rarely if you select an appropriate value in -o switch.

Time to time I look through the Atmel AVR Studio microcontroller description files and compare device signatures and fuses with Atmel datasheets. I noticed that the files have many programming parameters but have not any syncronisation method flag.

I checked AVR ISP mkII and AVR Dragon behavior and found out that both of them use SCK-pulse resynchronisation for all microcontrollers. Atmel datasheets don’t matter for Atmel programmers!

After that I decided to change resynchronisation procedure in AVReAl.

Starting from next release the procedure will be the same for all AVRs: SCK pulse will be used.

українська

українська english

english